MOVE, un processeur pas comme les autres

Il y a une architecture de processeur qui sort vraiment de l'ordinaire, le projet MOVE :

http://ce-serv.et.tudelft.nl/MOVE/index.html .

(NB: sur ce site, les fichiers les plus intéressants sont au format post-scritp ! Prévoir GOSTSCRIPT si vous êtes sur WINxxxxxx ! ) . C'est un processeur qui n'a qu'une instruction : MOVE !

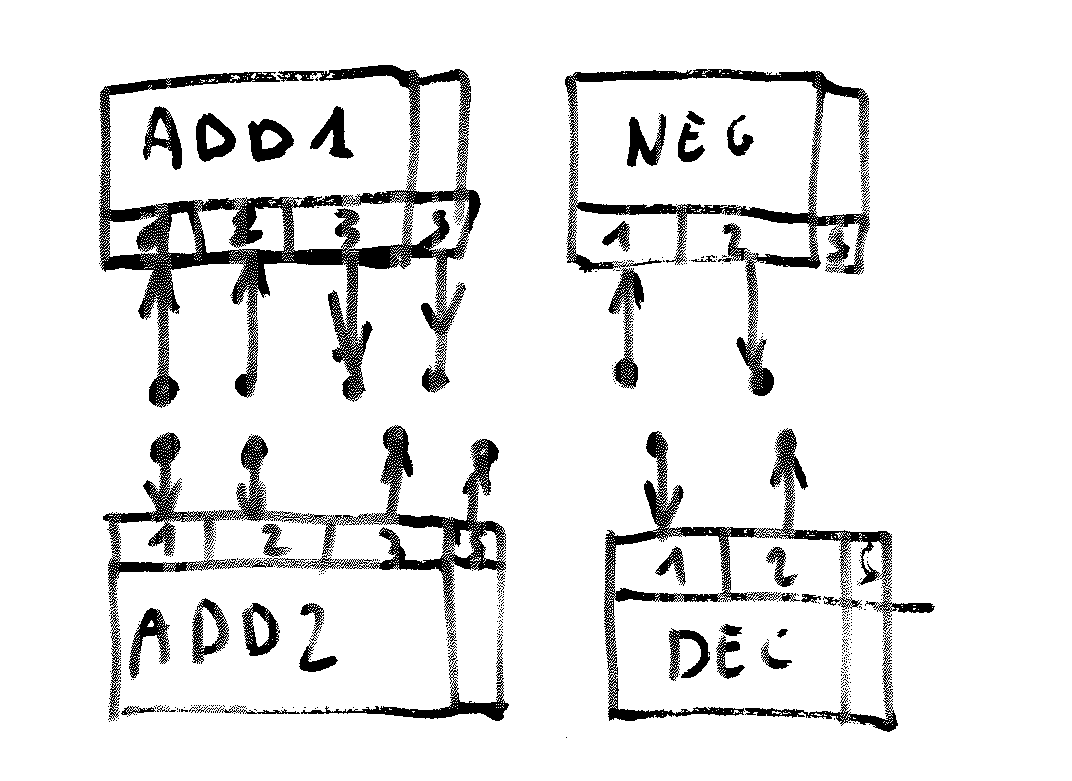

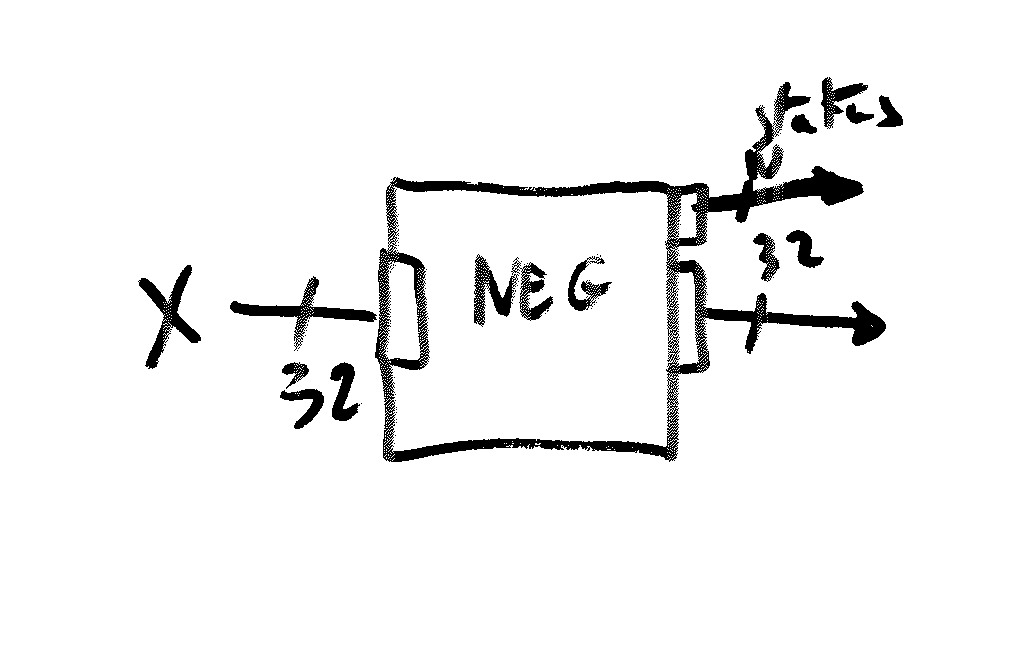

L'idée principale est de découper et d'étaler les fonction des ALUs sur plusieurs adresses.

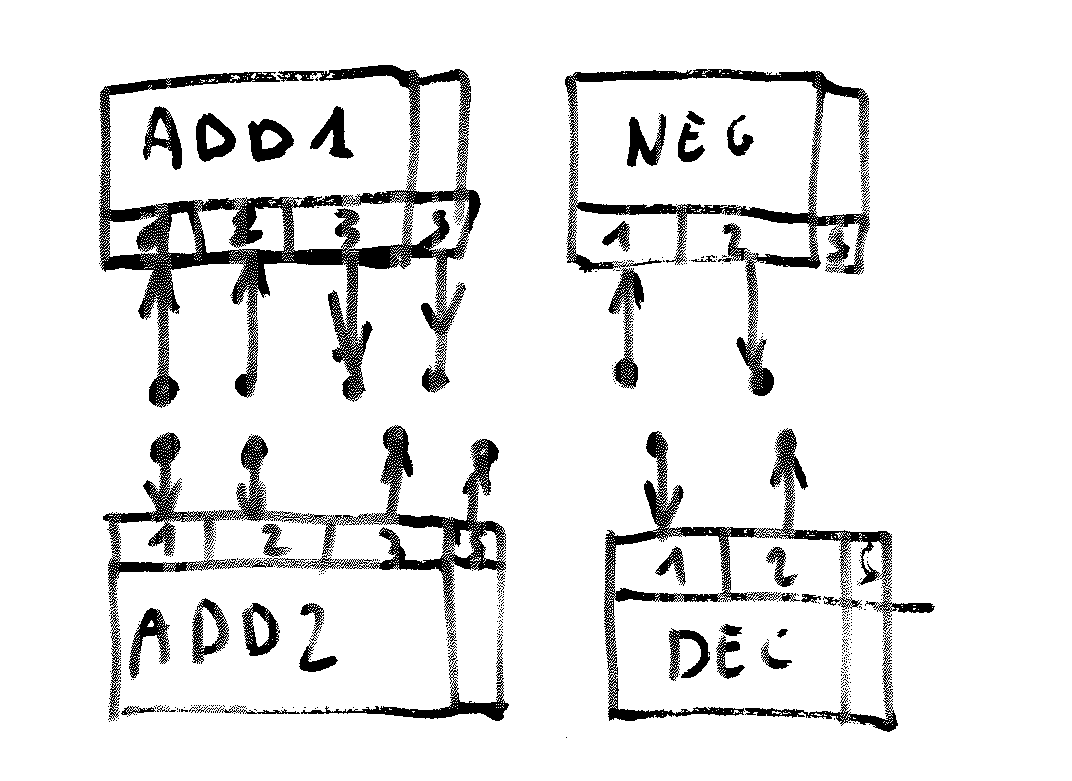

Par exemple, pour faire Z = (X and Y) (ci-dessus), on charge les opérandes X et Y dans l'opérateur AND n°1 (on peut supposer que le processeur peut en comporter plusieurs) : X->AND(1,1) ; Y->AND(1,2) , le résultat est alors présent sur la sortie de l'opérateur AND(1) à une adresse connue. On peu l'utiliser comme telle ou charger le registre Z du résultat AND(1,3)->Z .

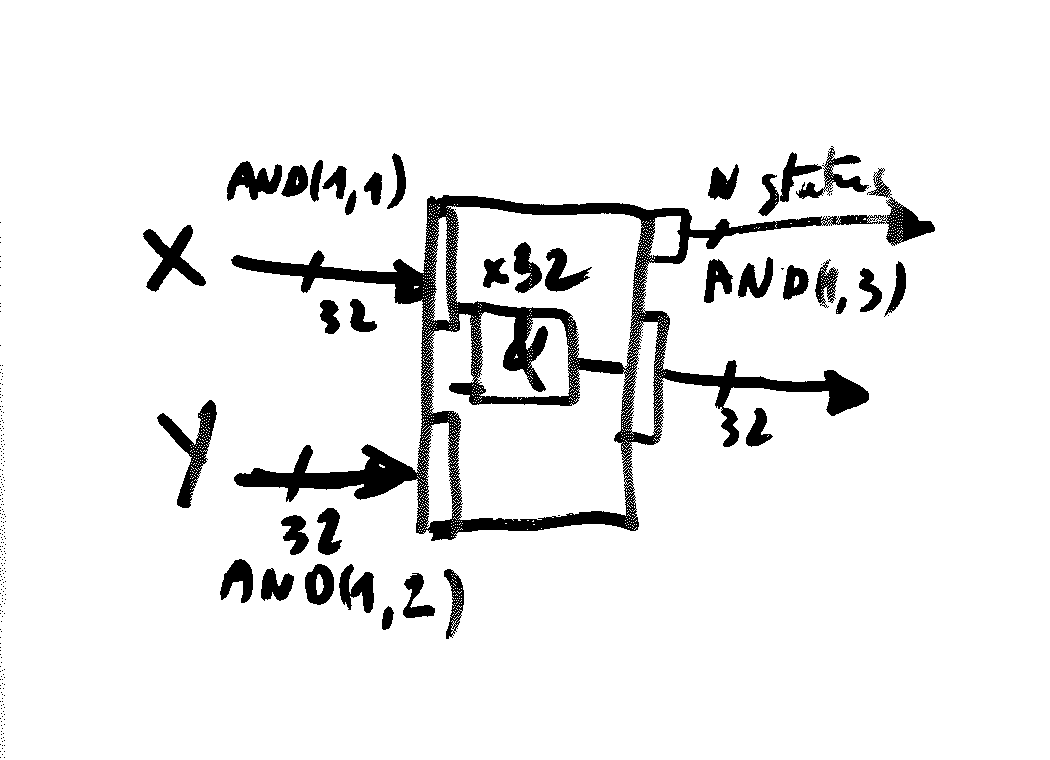

C'est encore plus simple pour une opération à un seul opérande, par exemple NEG (ci-dessus, sur 32bits ), le complément à deux de X : X->NEG(1,1) le résultat est dans NEG(1,2) . On peut choisir un bus de 16 ou 32 bits pour les données, et 64 bits voir plus (128, 256, 1024, ... ) pour les instructions de manière à faire N opérations indépendantes simultanément. C'est le but !

On ne peut pas relier toutes les sorties à toutes les entrées en même temps, car la densité des connections serait trop grande. Il faut les limiter et adopter des configurations similaires à celles des réseaux conventionnels. Une des plus intéressantes est le réseau « téléphonique » . N sources sont à connecter à M destinations, ce qui nécessiterait NxM connections. On se limite à K connections (K<<NxM) . Ces procédés sont bien décris dans http://ce-serv.et.tudelft.nl/MOVE/papers/Corporaal99a.ps.gz .

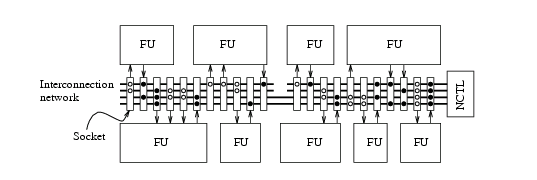

(voir exemple ci-dessous, tiré du site MOVE ; FU= unité fonctionnelle et NTCL= contrôleur d'aiguillage vers les registres ; chaque point représente la possibilité d'une connexion )

Ce type de processeur appartient donc à la famille des VLIW (Very Long Instruction Words ), comme le nouvel Intel 64 bit ! Comme tous ces cpu's, le rôle du compilateur est essentiel. C'est lui qui est chargé d'optimiser la « parallellisation » des instructions. Si il est mal conçu, toute la puissance est gaspillée ! Mais contrairement à la plus part des VLIW's, MOVE a des instructions à la « RISC », c'est à dire simple, faites en un seul cycle machine, ne nécessitant pas de micro-programme. Chaque portion du mot d'instruction de 64 bits (ou plus ) code directement une fraction du travail à faire

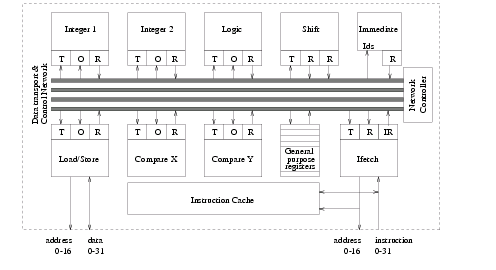

A l'université de Delf, des chercheurs étudient ce type de processeur. Ils ont fait des prototypes sur silicium, notamment un processeur de 32 bits pour les données et 64 bits pour les instructions, le MOVE32INT (voir ci-dessous).

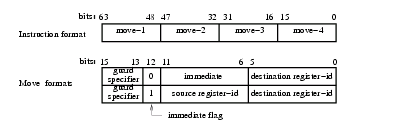

Ci-dessous le format des instructions :

Chaque instruction est codée sur 16 bits, 6 bits pour la source et autant pour la destination , les 4 restants pour le contrôle.

Il a été fabriqué avec la technologie MOS 0,2µ et est cadencé à 80MHz (rien à voir avec les possibilités industrielles actuelles ) . Les ALUs sont quadruplées, (pas d'opération en virgule flottante) et permet 4x80M,op/sec soit 320M.op/sec (voir http://ce-serv.et.tudelft.nl/MOVE/papers/EuroMicro2.ps.gz ) . Ces performance sont très prometteuses !

Le compilateur gnu GCC a été adapté à ce MOVE32INT. Les auteurs disent assez peu de choses à propos de portage et le niveau d'optimisation du code que l'on peut atteindre ...

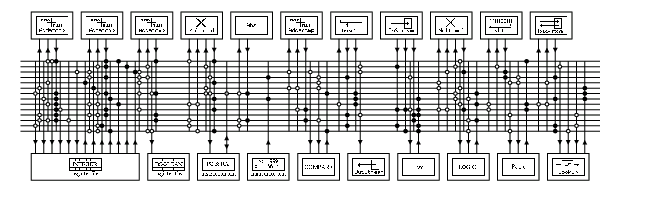

Ci-dessous un exemple de ce que pourrait être un processeur TTA spécialisé de la traitement de signal audio-vidéo :

Là, on dispose de FUs complexes (multiplication, FFT, convolution, ...)

Plus modestement, on peut faire un projet personnel de cpu TTA. On peut le cadencer à 1Mhz et faire les ALUs et autres FUs avec des EPROMs combinées avec des 74lsxxx ... Le séquenceur peut être simple car il n'y a qu'une vraie instruction (move) , les adresses directement codées par des tranches du mot à la « RISC ». Il n'est pas d'achitecture « Von Neuman » : bus d'intructions et de données séparés !

Un bus de données de 32 bits peut être envisagé pour les opérations simples. Il est facile d'étendre un tel processeur : il suffit de connecter de nouveaux FUs et registres, de le signaler au compilateur (donner les fonctions, adresses et aiguillages bien sur ) . Si la possibilité de codage dépasse la largeur du mot d'instruction, il est alors indispensable d'élargir le bus d'instruction d'un bloc voir de tout recoder ! Evidement, la compatibilité d'une version matérielle à une autre est difficile à maintenir sans recourir à une couche de micro-programmation très complexe. Il faut tout recompiler . Avec du LINUX et autre NETBSD c'est envisageable . Avec des systèmes fermés à la windows c'est impossible ... Des applications « grand public » de ce genre de cpu tta ne sont pas pour demain ...

Retour à la table des matières